# COMPARATIVE ANALYSIS OF MULTILEVEL INVERTER WITH AND WITHOUT TRANSFORMER

# Francesco Russo1\*, Giulia Conti2, Luca Benedetti3

<sup>1</sup>Department of Civil and Environmental Engineering, Politecnico di Milano, Milan, Italy <sup>2</sup>Department of Mechanical Engineering, Politecnico di Milano, Milan, Italy <sup>3</sup>Department of Mathematics, Politecnico di Milano, Milan, Italy

#### **ABSTRACT**

In this paper/thesis a comparative analysis of multilevel inverter with and without transformer through simulation is carried out. The output voltage and current waveforms are compared for resistive load without any filtering unit. Reduction in device count is also considered to reduce switching losses. In this paper/thesis, a novel cascaded transformer multilevel inverter is proposed. The number of the switching devices is reduced in the proposed topology. This topology comprises of a DC source, several single phase low-frequency transformers, two main power switches and some bidirectional switching devices. In this topology, only one bidirectional switch is employed for each transformer. However, in conventional cascaded transformer multilevel inverter, four switching devices are required for each transformer. Therefore, more output voltage levels can be obtained using fewer switching components. Reduction in the number of switching devices which also means reduction in the number of gate drivers results in smaller size and low implementation cost. Switching power losses are also reduced in this topology. Selective harmonic elimination (SHE) technique is applied to the proposed inverter to obtain a high quality output voltage. Simulation results are also provided to verify the feasibility of the proposed converter.

Keywords: CTIOS; Multilevel inverter; SHE, H-bridge.

#### I. INTRODUCTION

The multilevel inverter [MLI] is used for high voltage and high power applications. This inverter produce staircase (stepped) waveform from several different levels of DC voltage. It have lower voltage rating of devices, low harmonics distortion, high power quality waveforms, lower switching frequency and losses, higher efficiency, reduction of dv/dt stresses. Because of the above characteristics, it have a possibility of working with low speed semiconductors if its compared with the two-level inverters. Many number of MLI topology are available but most popular MLI topology is diode clamped, flying capacitor and cascaded multilevel Inverter.

The multilevel inverter has been implemented in various applications ranging from medium to high-power levels, such as motor drives, power conditioning devices, also conventional or renewable energy generation and distribution. The different multilevel inverter structures are cascaded H-bridge, diode clamped and flying capacitor multilevel inverter [1].

For high voltage applications, two or more power switches can be connected in series in order to provide the desired voltage rating. However, the characteristics of devices of the same type are not identical. For the same OFF state current, their OFF state voltages differ. Even during the turn OFF of the switches the variations in stored charges cause difference in the reverse voltage sharing. The switch with the least recovered charge faces the highest transient voltage. For higher current handling, the switches are connected in parallel, however because of uneven switch characteristics the load current is not shared equally [2].

The operation of a multilevel inverter is concerned with comparison of carrier and reference wave.

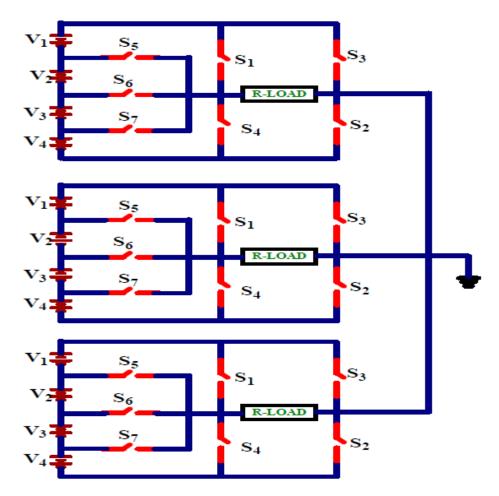

Figure 1: Power Circuit for Three Phase Nine Level Inverter

The basic operation can be described as an optional stacking of a number of DC voltage source stages which depends on certain time of operation that one stage is stacked (forward or reverse) or bypassed. MLIs also have some issues such as requiring a big number of semiconductor switches which increases as the number of steps/levels increases. If the levels of the steps increase the design will be complex for synchronous gate drivers for different levels. The order of numbering of the switches is S1, S2, S3, S4, S5, S6 and S7. This circuit does not have a capacitor and diode. So cost of the circuit is low compared to the conventional circuit. The voltage levels of the outputs are 4Vdc, 3Vdc, 2Vdc, Vdc, 0, - Vdc, -2Vdc, -3Vdc, -4Vdc. In proposed circuit semiconductor switches are less when compared to the conventional circuit. So the advantages of the proposed circuit are less cost and minimum switching losses. Figure 1 shows a three phase nine level Inverter.

At desired frequency and voltage, the conversion of input DC supply into the AC supply with help of semiconductor power switches is takes place in the conventional two level inverters. Depend upon on the configuration; four or six switches are used. A group of switches provide the positive half cycle at the output which is called as positive group switches and the other group which supplies the negative half cycle is called negative group switches. A detailed comparison is made between the conventional inverter and multilevel inverter as shown in Table 1.

Table 1: Comparison of Conventional Two Level Inverter and Multilevel Inverter

| Those It comparison of conventional two zeros inverter and intention |                     |  |

|----------------------------------------------------------------------|---------------------|--|

| Conventional Inverter                                                | Multilevel Inverter |  |

|                                                                      |                     |  |

## Haut | ISSN: 0938 - 2216 | Vol. 22, Issue 7 | 2024

| Higher THD in output voltage                                      | Low THD in output voltage                                                      |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Switching stresses are more on the devices                        | Switching stresses reduces on the devices                                      |

| High voltage applications it is not applicable                    | It is applicable for high voltage applications                                 |

| Higher voltage levels of output are not produced                  | Higher voltage levels of output are produced                                   |

| Since dv/dt is high, the EMI for system is high                   | Since dv/dt is low, the EMI for system is low                                  |

| Higher switching frequency is used hence switching losses is high | Lower switching frequency can be used and hence reduction in switching losses. |

| Power bus structure, control schemes are simple                   | Control scheme becomes complex as number of levels increases                   |

| Reliability is high                                               | Reliability can be improved, rack swapping of levels is possible               |

In the field of high voltage and high power applications the tremendous attention is drawn by multilevel inverter in recent past. Determination of their control strategies is the emerging topic in the research based on the multilevel inverter. The most important problems are associated with controlling of a multilevel voltage source inverter to obtain the variable amplitude and frequency in sinusoidal output by employing simple control techniques. Non fundamental current harmonics surely cause power losses, electromagnetic interference and pulsating torques in AC motor drives in voltage source inverter. With any switching strategy, harmonic reductions are strictly related to the performance of an inverter. With respect to the reduction in power quality, various Pulse Width Modulation control schemes have been developed in multilevel voltage source inverter

#### II. STATEMENT OF PROBLEM

Higher frequencies are employed in traditional pulse width modulation methods because of the undesirable harmonics occur at higher frequencies, which can be filtered easily and several kHz is well above the acoustic noise level. But, the traditional pulse width modulation methods cause electromagnetic interference (EMI). The rapid change in voltage (dv/dt) is the cause of electromagnetic interference. A high dv/dt produces common-mode voltages across the windings of motor and leads to damage. In multilevel inverters, as the switching involves several small voltages, the rapid change in voltage is smaller. Further, switching at the fundamental frequency will also result in decreasing the number of times these voltage changes occur per fundamental cycle. But harmonic elimination is the major issue for multilevel inverters. The harmonic elimination in multilevel inverters have been proposed in this thesis for the following reasons.

- ❖ Harmonics in output voltage create power losses in equipments.

- ❖ Harmonics are the source of electromagnetic interference (EMI).

- The protecting devices like snubber circuits and filters have to be incorporated in the designed circuits for the elimination of harmonics. Hence cost of the circuits becomes more

- Electromagnetic interference can interfere with control signals used to control the power electronic devices and radio signals.

- ❖ The harmonics can create losses in power equipments.

#### III. PROPOSED SYSTEM

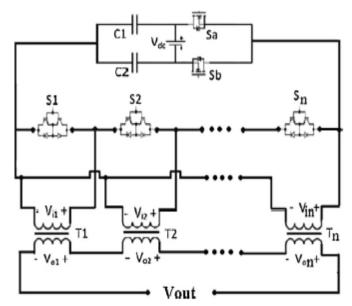

The novel topology and new topologies introduced for transformer based multilevel inverters are compared. Traditional cascaded H-bridge cells multilevel inverter needs several numbers of semiconductors and separated DC sources, these several numbers of isolated sources and components are difficult to be provided and controlled so this

is a serious drawback for this topology. To eliminate need for several isolated DC sources the cascaded transformer H-bridge

Multilevel was introduced in which the transformers are used instead of DC sources. Attempting reach to a less component topology and obtain an optimized topology have led to appear some new topology which utilize fewer semiconductors and DC sources. Cascaded transformer inverter with one DC sources (CTIOS) is one of the newest less component topologies of transformer based multilevel inverter which have been introduced.

Figure 2: Cascaded Transformer H-bridge Multilevel Inverter with Single DC source

- (i) A cascaded transformer multilevel inverter with reduced number of switching components will be presented.

- (ii) The proposed topology utilizes low-frequency single-phase transformers and a DC voltage source.

- (iii) This configuration can reduce the number of switches in comparison with conventional cascaded transformer multilevel inverters.

- (iv) Selective harmonic elimination technique is applied to mitigate the low order harmonic components.

## IV. SIMULATION ANALYSIS AND RESULT

In this section we will focus on the topology of only Cascaded H-bridge multilevel inverter as it has more advantages with respect to the other two topologies i.e. the diode clamped multilevel inverter and the flying capacitor multilevel inverter

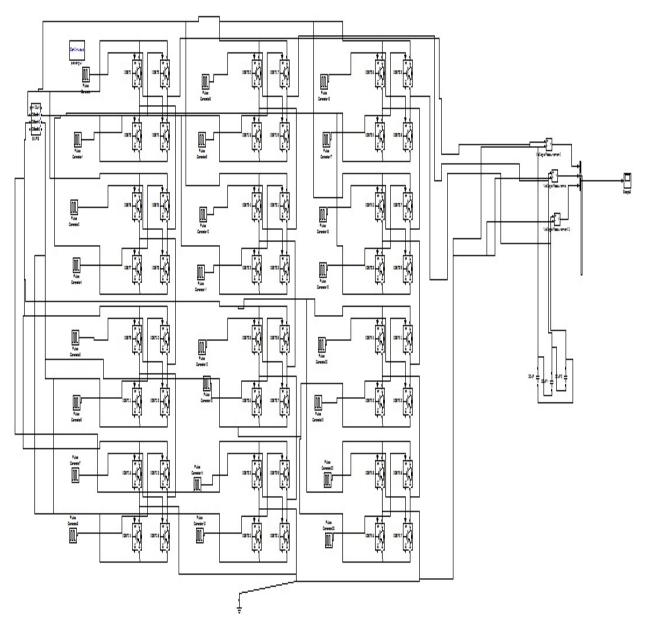

#### Modelling of Nine Level Cascaded H-Bridge Multilevel Inverter

In this type of multilevel inverter we will get nine levels of output voltage. The voltage generated at the output of the multilevel inverter. Nine level voltage output is achieved with reduced value of THD & hence the overall power quality of the system is improved. For further reduction of THD shunt capacitor filter is also used at the output side of MLI.

Figure 3: Simulink model of 9 level Cascaded H-Bridge multilevel inverter

Simulation Results of Cascade H Bridge Multilevel Inverter

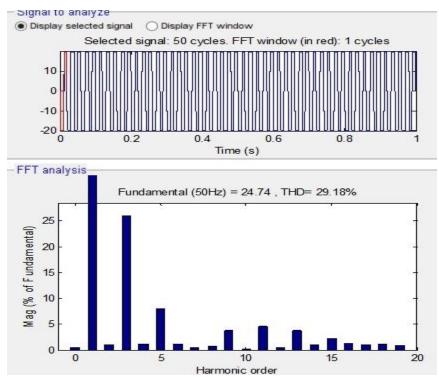

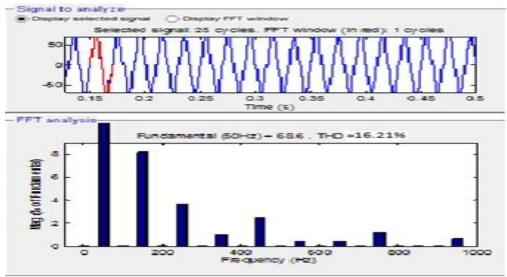

Figure 4: THD analysis of 5 level Cascaded H-Bridge MLI

Figure 4 shows the THD analysis of 5 level cascaded H-bridge MLI in which the THD value is found to be 29.18%. This value matches with the IEEE standards of tolerance level of  $\pm$  5%.

Figure 5: THD analysis of 9 level Cascaded H-Bridge MLI

Figure 5 shows the THD analysis of 9 level cascaded H-bridge MLI in which the THD value is found to be 16.12%. This value matches with the IEEE standards of tolerance level of  $\pm$  5%.

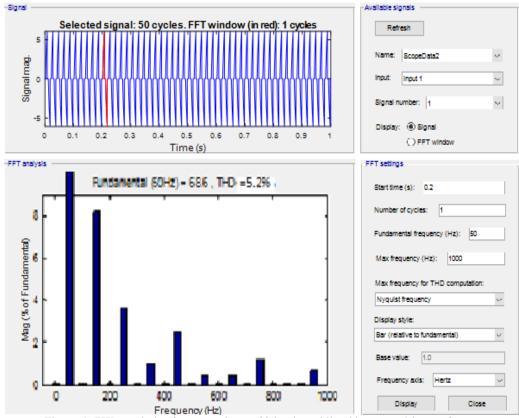

Figure 6: THD analysis of output voltage of 9 levels multilevel inverter with transformer

The simulation of cascade with transformer multilevel of 9 levels without filter as in figure 5.7 has been done by using MATLAB SIMULINK. Harmonic investigation is performed using THD analysis of the inverter output voltage shown in figure 5. 10. THD is observed as 5.2%

### Comparison of THD Values of Different Levels of Multilevel Inverter

The THD of 5 level,9 level & 15 level cascaded H-bridge multilevel inverter is observed .The THD for 5 level cascaded H-bridge is found to be 29.18%, for 9 level it is calculated 15.12% & for 15 level it is calculated 4.9%. The comparison is given in table 2. For further reduction of THD shunt capacitor filters are also used. This value matches with the IEEE standards for THD.

In this section the THD values of cascaded H-bridge multilevel inverter with and without using filtering unit is performed. In the comparison we found that the percentage THD values of 5 level, 9 level and 15 level multilevel using shunt capacitor filter comes to 29.18%, 15.12% & 4.9% respectively & percentage THD values of 5 level, 9 level and 15 level multilevel inverter without using filter comes to 29.18%, 16.12% & 5.2% respectively.

| Table 2.  | Comparison of | f THD values of  | f different levels o | f multilevel inverter | for SAPS system      | with & without filter |

|-----------|---------------|------------------|----------------------|-----------------------|----------------------|-----------------------|

| I uvic 2. | Companison o  | i iiid vaaaes oi | uniterent tevets o   | i munineven mvenen    | ווטו טאנט כו בבע ועו | with & without filler |

| Tuble 2. Comparison of 111D values of adjerent levels of maddlevel inverter for SALS system with & without full |   |                                |                                |  |

|-----------------------------------------------------------------------------------------------------------------|---|--------------------------------|--------------------------------|--|

| S.No Levels                                                                                                     |   | Percentage THD of MLI for SAPS | Percentage THD of MLI for SAPS |  |

|                                                                                                                 |   | System With Filter             | System Without Filter          |  |

|                                                                                                                 |   |                                |                                |  |

| 1                                                                                                               | 5 | 29.18                          | 29.18                          |  |

|                                                                                                                 |   |                                |                                |  |

# Haut | ISSN: 0938 - 2216 | Vol. 22, Issue 7 | 2024

|   | 2 | 9  | 15.12 | 16.21 |

|---|---|----|-------|-------|

| • | 3 | 15 | 4.9   | 5.2   |

Also the THD of 9 level transformer employed multilevel inverter with single DC source is observed as 5.21% which is less compared to novel 9 level cascade H bride Multilevel inverter. Also there is reduction in device count to achieve same voltage levels. The detailed comparison using transformer in multilevel inverter is shown in table 2.

Table 3: Comparative analysis of 9 level cascade multilevel inverter with and without transformer

| S.NO. | Parameters                   | Cascade Multilevel<br>Inverter with<br>Transformer | Cascade Multilevel<br>Inverter without<br>Transformer and<br>filtering Unit. |

|-------|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|

| 1.    | THD levels                   | 5.2%                                               | 16.21%                                                                       |

| 2.    | DC source required           | Over all single source                             | 1 Source for each bridge                                                     |

| 3.    | Main Switches                | 8                                                  | 12                                                                           |

| 5     | Reliability during switching | Yes                                                | No                                                                           |

#### V. CONCLUSION

This paper presented a new version of cascaded multilevel inverter, which employed a single dc input source and low frequency three-phase transformers. Performance of the proposed CMI is investigated with three switching techniques namely, fundamental frequency switching and selective harmonic elimination SHE approach.

The proposed topology utilizes low-frequency single-phase transformers and a DC voltage source. This configuration can reduce the number of switches in comparison with conventional cascaded transformer multilevel inverters. From the simulation we have observed that as THD of conventional cascade Multilevel inverter even with filtering unit is obtained as 16.21% while the THD of transformer based Multilevel inverter is observed as 5.2% quit lesser as compared to without transformer employed inverter. THD can be further reduced by increasing the level. The inverter having lesser THD will be use for renewable energy applications. Selective harmonic elimination technique is applied to mitigate the lowered harmonic components. In order to verify the operation and performance of the proposed inverter, simulation and experimental results using a single-phase 9-level multilevel inverter prototype are provided.

#### REFERENCES

- 1. Colaka Ilhami, Kabalcib Ersan , Bayindira "Review of multilevel voltage source inverter topologies and control schemes", Energy Conversion and Management

- 2. Volume 52, Issue 2, February 2011, PP 1114-1128

- 3. Divya Subramanian, Rebiya Rasheed "Five Level Cascaded H-Bridge Multilevel Inverter Using Multicarrier Pulse Width Modulation Technique", International Journal of Engineering and Innovative Technology (IJEIT) Volume 3, Issue 1, July 2013, pp 428-441

- 4. J. Rodriguez, J.-S. Lai, and F. Z. Peng, —Multilevel inverters: A survey of topologies, controls, and applications, IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002

- 5. M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, —A Survey on cascaded multilevel inverters, IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197-2206, July 2010.

# Haut | ISSN: 0938 - 2216 | Vol. 22, Issue 7 | 2024

- 6. M Murali, A Arulmozhiyal and P Sundaramoorthy, A Design and Analysis of voltage source inverter for renewable energy applications. Telkomnika Indonesian Journal of Electrical Engineering. 2014; 12(12): 8114-8119

- 7. J Jamaludin, N Abd rahim, Hew wooiping. Multilevel voltage source inverter with optimized usage of bidirectional switches. IET Power Electronics. 2015; 8(3): 378-390.

- 8. Gabriel HP Ooi, Ali I Maswood AI, Ziyou Lim. Five-Level Multiple-Pole PWM AC AC Converters with Reduced Components Count. IEEE transaction on industrial electronics. 2015; 62(8): 4739–4748.

- 9. J. Gafford, M. Mazzola, J. Robbins, and G. Molen, "A multi-kilowatt high-frequency ac-link inverter for conversion of low-voltage dc to utility power voltages," in Proc. IEEE Power Electron. Spec. Conf., 2008, pp. 3707–3712.

- 10. C. Y. Chen, Y. H. Lin, J. F. Chen, and R. L. Lin, "Design and implementation of DSP-based voltage frequency conversion system," in Proc. Int. Symp. Comput. Commun. Control Autom., May 2010, pp. 435–438.

- 11. E. Ozdemir, S. Ozdemir, and L. M. Tolbert, "Fundamental-frequency-modulated six-level diode-clamped multilevel inverter for three-phase stand-alone photovoltaic system," IEEE Trans. Ind. Electron., vol. 56, no. 11, pp. 4407–4415, Nov. 2009.

- 12. Jian Chen, XianglianXu, Shunjie Li, Ka Hu, Liang Yu, "Implementation of Grid-Connected Cascaded Multi-Level Inverter Based on FPGA for Centralized Photovoltaic Generation".

- 13. Hirofumi Akagi, "Classification, Terminology, and Application of the Modular Multilevel Cascade Converter (MMCC), "IEEE Transactions On Power Electronics, Vol. 26, No. 11, November 2011.